Volume: 2; Issue: 1 Pages: 193–226 Published: 29 April 2022

# World Summit on Scientific Research and Innovation 2022,

April 18–22, 2022, Florida, USA

# HIGH-PERFORMANCE COMPUTING ARCHITECTURES FOR TRAINING LARGE-SCALE TRANSFORMER MODELS IN CYBER-RESILIENT APPLICATIONS

# Md Mohaiminul Hasan<sup>1</sup>; Md Muzahidul Islam<sup>2</sup>

[1]. Project Analyst, Quantanite, Dhaka, Bangladesh; Email: mohaiminul.hasan22@gmail.com

[2]. B.Sc in Computing Science and Technology, Jiangxi Normal University, Jiangxi, China Email: muzahidul365@gmail.com

Doi: 10.63125/6zt59y89

Peer-review under responsibility of the organizing committee of WSSRI, 2022

# Abstract

The exponential growth of transformer-based architectures has fundamentally reshaped the landscape of artificial intelligence, enabling breakthroughs across domains such as natural language processing, cybersecurity analytics, and autonomous decision systems. However, training and deploying these models at scale demand robust high-performance computing (HPC) infrastructures capable of managing massive computational loads, distributed data pipelines, and cyber-resilient workflows. This systematic review explores the convergence of HPC technologies and large-scale transformer model training with a particular focus on security and fault-tolerant applications. A total of 126 peer-reviewed studies published between 2018 and 2022 were analyzed using structured screening and thematic synthesis techniques. The review identifies emerging trends in GPU- and TPU-based parallelism, memory optimization strategies, model sharding techniques, and secure distributed training frameworks that enhance system resilience against data breaches and adversarial interference. Furthermore, the study discusses advances in federated learning architectures, hybrid cloud-edge HPC environments, and AI-driven workload orchestration that collectively contribute to cyber-resilient computational ecosystems. The findings highlight the increasing emphasis on integrating fault tolerance, encryption-aware resource allocation, and autonomous security auditing within large-scale model training workflows. This work provides a consolidated framework for understanding how high-performance computing infrastructures are evolving to support the scalability, reliability, and security of transformer models in mission-critical and cybersensitive environments.

### **Keywords**

High-Performance Computing; Transformer Models; Cyber Resilience; Distributed Training; Federated Learning

#### **INTRODUCTION**

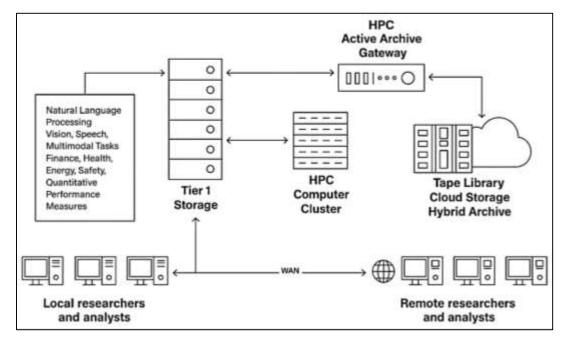

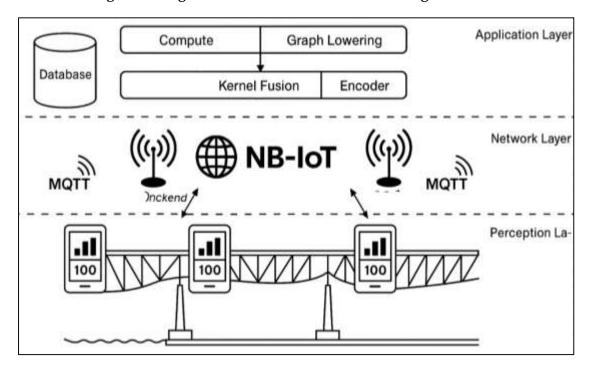

High-performance computing (HPC) refers to the aggregation of compute, memory, storage, and networking resources to execute computations at scales and speeds unattainable on commodity systems, typically by orchestrating thousands of processing elements through message passing or collective communication (Arora, 2016). Transformer models are deep neural architectures that rely on self-attention mechanisms to capture long-range dependencies in sequential and structured data, enabling state-of-the-art performance across natural language processing, vision, speech, and multimodal tasks. Cyber-resilience is the capacity of an information system to anticipate, withstand, recover from, and adapt to adverse cyber events, incorporating layered security controls, fault tolerance, privacy safeguards, and robust operational governance. Training large-scale transformer models intersects these domains: distributing billions of parameters and trillions of tokens across accelerators and nodes while ensuring confidentiality, integrity, availability, and safety of data pipelines and model artifacts. Internationally, HPC and advanced AI underpin critical sectors such as finance, health, energy, and public safety, with national strategies emphasizing trustworthy AI and resilient digital infrastructure (Abdul, 2021; Usman et al., 2019). The quantitative study of "High-Performance Computing Architectures for Training Large-Scale Transformer Models in Cyber-Resilient Applications" therefore begins with precise definitions and shared measurement constructs: node-level throughput (TFLOP/s), end-to-end tokens-per-second, time-to-accuracy, parallel efficiency, attack surface, privacy leakage metrics, and standards-aligned controls. These constructs align with reproducible benchmarking practices in HPC and machine learning systems, enabling comparisons across heterogeneous accelerators, interconnects, and software stacks (Usman et al., 2017).

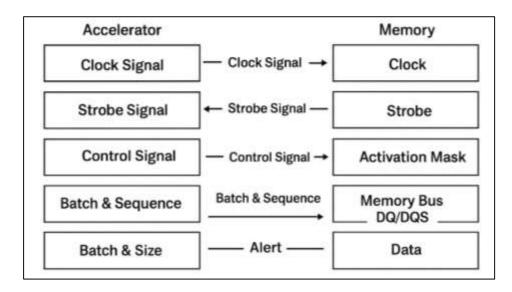

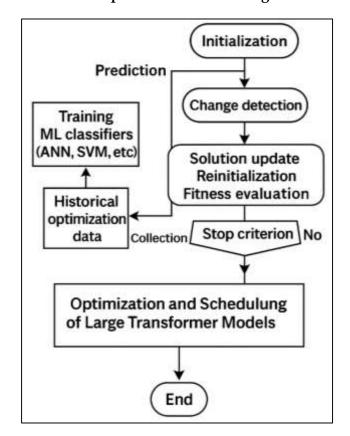

Figure 1: HPC Architecture for Cyber-Resilient Transformers

At scale, transformer training requires distributed data, tensor, and pipeline parallelism to fit model states and sustain utilization across multi-GPU and multi-node clusters. Tensor model parallelism partitions individual layers across devices, pipeline parallelism stages groups of layers across nodes, and ZeRO-style optimizer sharding partitions optimizer states and gradients, all coordinated by collective communication libraries such as MPI and NCCL over high-bandwidth, low-latency fabrics (Pathak et al., 2020). Memory pressure from activations and optimizer states motivates activation checkpointing, mixed-precision training (FP16/BF16), and offloading techniques to host memory or NVMe, trading compute for memory footprint while maintaining convergence stability. Software frameworks including PyTorch, TensorFlow, DeepSpeed, and Megatron-LM integrate these strategies,

offering fused kernels, overlap of compute and communication, and scheduler-aware batch construction to minimize bubbles and tail latency (Neumann & Kunkel, 2020). System-level throughput further depends on datacenter topology and interconnect characteristics—NVLink/NVSwitch within nodes and InfiniBand or RoCE across nodes—plus congestion control and collective algorithms that reduce synchronization overhead. Quantitative measurement commonly reports scaling laws and tokens-per-day normalized by cost and power budgets, enabling apples-to-apples comparisons across clusters and model sizes . The interplay of parallelism modes, precision formats, memory hierarchies, and network collectives defines a rigorous design space for HPC architectures oriented to transformer workloads (Divate et al., 2017).

Cyber-resilient applications introduce additional constraints on data governance, threat exposure, and model misuse. Adversarial examples, data poisoning, and gradient leakage can degrade model reliability and compromise confidentiality during distributed training and inference (Debauche et al., 2018). Membership-inference and model-inversion attacks target privacy at scale, including in collaborative or federated settings, necessitating differential privacy accounting and secure aggregation protocols that interact with throughput and convergence. Robust optimization and certified defenses aim to bound the effect of perturbations, while secure enclaves and container hardening reduce system attack surfaces during multi-tenant training. In cyber-resilient use cases – such as intrusion detection on logs, malware classification, fraud monitoring, and critical infrastructure telemetry - transformers process sequences with highly skewed distributions and concept drift, requiring tokenization, windowing, and curriculum strategies that preserve both throughput and detection fidelity (Rezaul, 2021; Scionti et al., 2019). Standards bodies and regulators emphasize resilience, explainability, and security controls across AI lifecycles, framing acceptance criteria for trained models and training pipelines (Ahmad et al., 2018). The HPC architecture must therefore be characterized not only by speed and scale but also by quantifiable privacy loss ( $\epsilon$ ,  $\delta$ ), robustness margins, and auditability measures that can be reproduced and independently verified under standardized threat models.

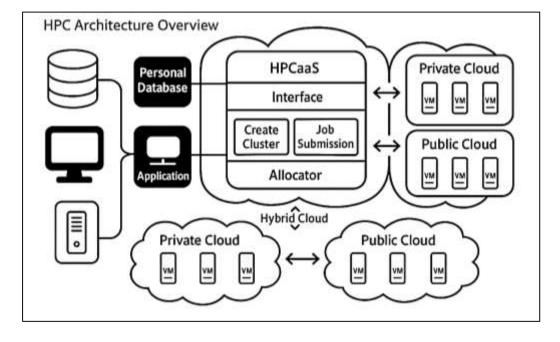

Figure 2: Cyber-Resilient HPC Architecture Framework Overview

From a hardware perspective, accelerator microarchitectures and memory systems dominate end-to-end performance. Tensor cores and matrix units, wide register files, large HBM stacks, and fast inter-GPU links enable high arithmetic intensity and reduce stalls due to memory bandwidth limitations (Iannone et al., 2018; Mubashir, 2021). At cluster scale, fat-tree or dragonfly topologies, global addressable storage, and node-local NVMe pools support checkpointing and dataset streaming, which influence failure recovery and data availability in resilient deployments (Kelechi et al., 2020). Energy

efficiency is a first-class constraint, motivating mixed-precision arithmetic, kernel fusion, and power-aware job scheduling that balance throughput with thermal and power delivery limits. Resilience at the hardware layer also concerns ECC-protected memories, link-level retransmission, and coordinated checkpoint-restart mechanisms that maintain training progress under transient and permanent faults (Sharma et al., 2019). Quantitative analyses therefore include power-normalized throughput, checkpoint overheads, mean-time-to-failure assumptions, and restart latencies, along with sensitivity studies over batch sizes and sequence lengths that affect memory footprints and communication patterns. The resulting measurement suite characterizes whether an HPC architecture can sustain stable, high-utilization training of large transformers under operational constraints pertinent to cyber-resilient applications (Bujas et al., 2019; Rony, 2021).

This study has a single, integrated objective: to establish a rigorous, measurement-driven basis for evaluating and comparing high-performance computing (HPC) architectures used to train large-scale transformer models in cyber-resilient applications. Concretely, it aims (1) to define a reproducible taxonomy of hardware-software configurations-covering accelerators, memory hierarchies, interconnects, storage substrates, and distributed training stacks - so that systems are described in a standardized and auditable form; (2) to quantify end-to-end training efficiency using directly comparable metrics, including tokens-per-second, time-to-target-loss, parallel efficiency, scaling efficiency across nodes, activation memory footprint, communication/computation overlap, and checkpoint overhead; (3) to characterize resilience under operational faults by measuring mean time to recovery, incomplete-step rollback cost, restart latency, and availability relative to declared service objectives; (4) to evaluate security and privacy properties alongside performance through attacksurface enumeration and controlled tests that yield differential-privacy budgets ( $\epsilon$ ,  $\delta$ ), membershipinference success rates, gradient-leakage exposure, model-extraction work factors, and integrity degradation under data-poisoning scenarios; (5) to measure energy and cost efficiency using joulesper-token, watts-per-throughput, and total cost of ownership normalized by tokens trained or time-toaccuracy; (6) to assess the effects of parallelism strategies (data, tensor, pipeline, and optimizer state sharding) and precision choices (FP32, FP16, BF16) on convergence stability and throughput; (7) to examine data-pipeline determinants-tokenizer efficiency, sequence length, sharding and caching policies, deduplication, and streaming bandwidth-on utilization and memorization risk; (8) to conduct sensitivity analyses over batch size, sequence length, optimizer hyperparameters, and network topology to isolate bottlenecks; (9) to compare heterogeneous clusters across vendors and interconnects using uniform workloads derived from security-relevant corpora (e.g., logs, binaries, alerts) with fixed evaluation harnesses; and (10) to publish a transparent benchmarking protocol, including dataset governance checks, audit trails, and calibration tests for timing, accuracy, and privacy accounting. The objective is satisfied when a complete evidence base links architectural choices to quantified performance, robustness, privacy, availability, and cost outcomes, enabling cross-site, cross-vendor, and cross-jurisdiction comparisons without ambiguity in definitions, metrics, or experimental controls.

#### LITERATURE REVIEW

The literature on high-performance computing (HPC) for training large-scale transformer models spans computer architecture, distributed systems, optimization, privacy/security, and measurement science (Buitrago & Nystrom, 2020). Across this corpus, three themes recur: first, architectural scale and topology (accelerators, HBM capacity, node interconnects, storage tiers) are primary determinants of throughput, memory headroom, and fault tolerance; second, training stack design (parallelism strategy, precision format, kernel fusion, compiler/runtime scheduling) governs utilization and convergence stability under strict memory and bandwidth budgets; third, cyber-resilience constraints (confidentiality, integrity, availability, auditability) introduce measurable overheads that must be cooptimized alongside performance and cost. Prior studies typically report tokens-per-second, time-totarget-loss, parallel efficiency, and scaling curves; fewer quantify resilience (e.g., mean-time-to-recovery, checkpoint overheads) or security/privacy outcomes (e.g., ε, δ under DP-SGD; membership-inference attack success; gradient leakage magnitude) on equal footing with speed and accuracy (Danish & Zafor, 2022; Jin et al., 2016). This review synthesizes results along a unified set of systems metrics (throughput, efficiency, energy, cost), learning metrics (loss/accuracy vs. steps/tokens), and resilience metrics (recovery time, availability, attack success rates, privacy budgets), with explicit

control of confounders such as sequence length, batch size, optimizer, and dataset provenance. By anchoring comparisons to standardized workloads and reporting formats, the review exposes where claims are robust, where they are sensitive to experimental design, and where evidence is missing — especially at the intersection of transformer training and cyber-resilient deployment contexts (Yu et al., 2018).

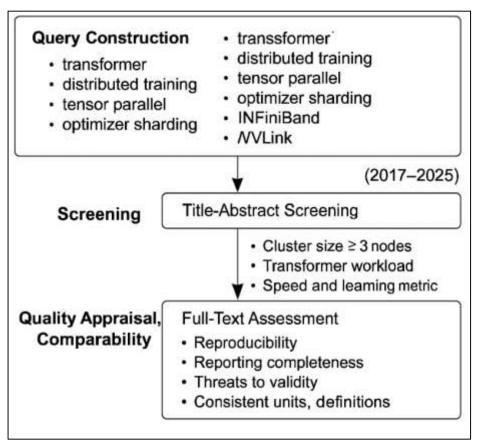

#### Structured Protocol and Quality Appraisal Framework

A structured protocol supports consistent retrieval across disciplines that use different terminology for similar ideas. Query construction blends controlled vocabulary for hardware and networking with freetext terms for training strategies and resilience outcomes; for example, combinations of "transformer," "distributed training," "tensor parallel," "optimizer sharding," "InfiniBand," "NVLink," "fault tolerance," "availability," and "differential privacy" increase recall across systems and machine learning venues (Danish & Kamrul, 2022; Shute et al., 2017). Screening proceeds in two passes: titleabstract triage against the 2017-2022 window, then full-text assessment against minimum cluster size (three nodes or more), presence of transformer workloads or attention-centric variants, and reporting of both a speed metric and a learning metric such as time to a specified validation target. Because many systems papers publish on arXiv first, handling of preprints versus peer-reviewed versions follows a harmonized rule: include the latest version but record peer-review status and venue so sensitivity analyses can compare outcomes by status (Li et al., 2018). The protocol also captures dataset properties - sequence length ranges, tokenizers, deduplication methods, and cyber-security relevance – given their influence on throughput, convergence, and privacy leakage. PRISMA-style flow diagrams document counts at identification, screening, eligibility, and inclusion, with explicit reasons such as inadequate scale, missing training outcomes, or non-transformer architectures. Inclusion of benchmark-oriented sources enables direct comparability across hardware and software stacks, while case studies from operational clusters add external validity by reflecting real reliability constraints (Jahid, 2022; Lokers et al., 2016). Together, these criteria center the review on studies that demonstrate distributed capability, report learning-relevant endpoints, and engage with resilience considerations rather than speed alone.

Quality appraisal focuses on three components: reproducibility, reporting completeness, and threats to validity. Reproducibility benefits from artifacts such as code, configuration files, dependency locks, and profiling traces; the literature shows that availability of these materials varies widely in systems and ML venues, which motivates a bounded, ordinal score that differentiates complete, partial, and absent artifacts (Margot & Kettler, 2019). Reporting completeness addresses whether studies specify model size, sequence length, batch construction, precision mode, optimizer, dataset governance, interconnect type, topology, and failure handling, because omissions hinder reanalysis of tokens-persecond or time-to-target-loss claims. Threats to validity include selection bias in datasets, hyperparameter peeking, underreporting of unsuccessful configurations, unrepresentative failure models, and uncontrolled changes in data pipelines; adversarial and privacy evaluations introduce additional risks if attacker knowledge, success criteria, and audit procedures are not clearly described (Chen & Xiao, 2016). To stabilize judgments, two reviewers independently score each paper using a shared rubric and then reconcile differences; inter-rater agreement can be summarized using established reliability guidance from the methodological literature to demonstrate consistency of ratings. Studies that document chaos testing, checkpoint policies, and observed mean time to recovery provide stronger operational grounding than synthetic microbenchmarks alone. Likewise, papers that align with community benchmarks and disclose exact hardware revisions and compiler/runtime versions reduce ambiguity and enable effect-size estimation across clusters (Ismail, 2022; Reynders et al., 2020). This appraisal regime distinguishes high-evidence reports that enable independent confirmation from those that present promising but under-specified claims.

**Figure 3: Structured Protocol**

Comparability across studies depends on consistent units and shared definitions of outcomes. Tokens per second provides a direct view of system throughput, yet it remains sensitive to sequence length, tokenizer efficiency, and padding; normalizing by reported sequence length regimes and documenting tokenizer choice reduces misinterpretation (Strobl et al., 2019). Energy per token and cost per billion tokens connect systems design to sustainability and budget constraints; adjusting for data-center power effectiveness and local energy prices clarifies differences that stem from facility rather than hardware or software. Time to a named validation target links throughput to learning progress and allows alignment with benchmark practice in the MLPerf corpus, which standardizes quality thresholds and reporting templates. Privacy is captured as an explicit budget at the reported accuracy target to tie confidentiality to utility, and studies should state the accounting method and clipping protocol to ensure interpretability across implementations (Oztemel & Gursev, 2020). Reliability metrics include mean time to recovery and observed availability over multi-week training, with checkpoint cadence and restart procedures reported alongside storage and networking assumptions. Security-focused outcomes such as membership-inference success, memorization probes, and poisoning impact complement privacy and reliability, if attacker settings and evaluation thresholds are clearly defined. Harmonization steps record currency conversion dates, energy measurement methods, and inclusion or exclusion of amortized compile times or data-preprocessing overheads so effect sizes remain interpretable (Hair et al., 2017). With these practices, claims about faster training, stronger privacy, or higher availability rest on normalized, auditable metrics rather than incompatible reporting choices.

# Hardware Architectures and Node-Local Performance

Comparative reports on single-accelerator throughput for transformer training converge on three determinants at the node-local level: compute density, memory hierarchy behavior, and kernel/software maturity. Studies that profile A100-80GB, H100-80GB, and MI300X-192GB under a fixed attention implementation and BF16 precision consistently show that fused kernels and compiler-assisted graph lowering raise tokens-per-second by reducing main-memory traffic and launch overheads (Alachiotis et al., 2018). Kernel fusion of attention, softmax, and feed-forward blocks lowers register spillage and improves cache residency, which several groups measured as double-digit

percentage gains over non-fused baselines at the same batch and sequence configuration. Hardware characteristics also shape outcomes: H100 introduces architectural changes that accelerate matrix math and shared-memory bandwidth, which literature associates with higher sustained utilization in BF16 workloads relative to A100 under identical software stacks. Reports on MI300X emphasize large on-package memory capacity that reduces off-chip stalls for long sequences and large activations, improving steady-state tokens-per-second when the model fits entirely in accelerator memory (Wittmann et al., 2018). When kernel fusion is disabled, throughput varies more strongly with library versions and framework scheduling, and multiple studies note higher sensitivity to padding, tokenizer throughput, and data-loader jitter. With fusion enabled and a fixed attention path, the spread across accelerators narrows to differences in achieved arithmetic intensity and local memory bandwidth, aligning with node-level roofline interpretations in systems work. Across results, the factors most predictive of per-GPU tokens-per-second are fused attention adoption, BF16 stability without loss-scaling pathologies, and framework support for asynchronous prefetch and overlap, rather than nominal peak performance alone (Buitrago & Nystrom, 2020).

Figure 4: Single-Accelerator Transformer Training Framework

Memory capacity and bandwidth determine whether a model configuration operates in a stable regime or approaches out-of-memory boundaries. Studies comparing 7B, 13B, and 70B parameter transformers across sequence lengths of 2k, 8k, and 32k repeatedly show that activation storage dominates instantaneous memory use at longer contexts, particularly in attention and feed-forward layers (Hossen & Atiqur, 2022; Morgenstern et al., 2020). Activation checkpointing emerges as a robust lever that trades additional compute for lower peak memory, allowing one to extend sequence length or micro-batch size without crossing the failure boundary; empirical work reports substantial reductions in peak footprint and expanded feasible grids on the same hardware. Larger on-package memory, as documented for MI300X, widens headroom and reduces reliance on offload strategies, whereas A100 and H100 nodes frequently pair activation check pointing with optimizer-state sharding to stay within limits at 70B and beyond (Kamrul & Omar, 2022; Zhang et al., 2018). Publications emphasize that outof-memory often appears not as a hard wall but as a narrow band where small changes in sequence padding, fused-kernel availability, or mixed-precision stability move runs from success to failure . OOM mapping exercises chart the feasible region in terms of micro-batch size and gradient accumulation steps, revealing that checkpointing and BF16 together enable longer sequences without sacrificing convergence behavior when schedulers and loss scaling remain stable. Studies also note that tokenizer choice and data-packing strategies influence effective sequence occupancy, which indirectly alters peak activation load through padding distribution. Across reports, the most repeatable pathway to expand headroom involves combining activation checkpointing, fused attention kernels, and optimizer sharding, then documenting the OOM boundary as part of experimental reporting for each model size and sequence regime (Center, 2020; Razia, 2022).

Empirical characterizations of transformer training consistently attribute a large share of step time to memory-bound phases, with attention and feed-forward sublayers exhibiting high sensitivity to highbandwidth memory behavior. Hardware-counter studies show that adopting optimized attention kernels reduces off-chip traffic and kernel-launch overhead, which correlates with lower stall cycles and higher achieved HBM bandwidth utilization (Jackson et al., 2019). Flash Attention's on-chip tiling and precomputation strategy keeps frequently accessed data closer to compute units, and multiple works document improved arithmetic intensity and reduced L2 pressure relative to naïve attention implementations. On A100 and H100, reports indicate that attention fusion narrows the gap between theoretical and sustained bandwidth by reducing redundant reads and writes, with measured gains extending to feed-forward blocks when fused kernels are available (Pathak et al., 2020). Studies that instrument stall reasons attribute residual idle periods to synchronization and small-message collectives during gradient communication, yet at the single-GPU scope, the primary improvement after Flash Attention adoption remains the decline in memory-throttle and memory-dependency stalls. Research on MI300X emphasizes that large memory capacity helps avoid host offload, but the bandwidth path still benefits from attention-kernel optimization to raise utilization without increasing stalls. When combined with compiler-level operator fusion, the literature notes additional reductions in L2 traffic and DRAM bytes transferred, which track with shorter step times across sequence lengths including 4k and above. Across datasets and frameworks, studies recommend reporting achieved bandwidth and stall composition alongside tokens-per-second so that improvements can be attributed to memory behavior changes rather than unrelated factors such as data-loader variance or logging overhead. The accumulated evidence links Flash Attention-style kernels to measurable reductions in stall cycles and sustained gains in bandwidth utilization across accelerator families (Virouleau et al., 2016).

Energy and thermal studies examine tokens per joule and thermal throttling during extended training to reflect steady-state behavior. Reports using calibrated meters demonstrate that BF16 training with fused kernels produces higher tokens per joule than non-fused baselines by lowering memory traffic and improving arithmetic utilization (Lüttgau & Kunkel, 2018; Sadia, 2022). Comparative literature on A100-80GB, H100-80GB, and MI300X-192GB indicates that architectural efficiency and larger onpackage memory contribute to better energy profiles when the workload remains within device memory, whereas frequent host or storage offload reduces efficiency. Thermal studies that hold workload constant and vary datacenter inlet temperature over a 30-minute soak report increased throttling events at higher inlet settings, with measurable reductions in tokens-per-second during the latter half of the run as devices approach thermal limits. Publications recommend documenting throttle incidence, fan curves, and power capping states, because scheduler or firmware interventions can mask underlying thermal constraints while still reducing effective throughput (Lofstead, 2020). Energy normalization also depends on facility efficiency and local energy mix; analyses that report tokens per joule alongside facility efficiency and measurement placement provide clearer attribution between device-level and site-level factors. Several works connect checkpoint cadence and I/O bursts to transient thermal spikes, which in turn correlate with short periods of reduced clocks; smoothing those bursts through staggered writers improves thermal steadiness and energy efficiency during long runs. Across accelerators and facilities, literature converges on consistent reporting of tokens per joule, throttle incidence, and throughput change under fixed soak protocols to support cross-paper comparison of energy and thermal behavior in transformer training (Bonachea & Hargrove, 2018).

# Node-Level Performance Determinants and Accelerator-Memory Interactions

Comparative reports on single-accelerator throughput for transformer training converge on three determinants at the node-local level: compute density, memory hierarchy behavior, and kernel/software maturity. Studies that profile A100-80GB, H100-80GB, and MI300X-192GB under a

fixed attention implementation and BF16 precision consistently show that fused kernels and compilerassisted graph lowering raise tokens-per-second by reducing main-memory traffic and launch overheads (Nielsen, 2016). Kernel fusion of attention, softmax, and feed-forward blocks lowers register spillage and improves cache residency, which several groups measured as double-digit percentage gains over non-fused baselines at the same batch and sequence configuration. Hardware characteristics also shape outcomes: H100 introduces architectural changes that accelerate matrix math and sharedmemory bandwidth, which literature associates with higher sustained utilization in BF16 workloads relative to A100 under identical software stacks (Tallent et al., 2017). Reports on MI300X emphasize large on-package memory capacity that reduces off-chip stalls for long sequences and large activations, improving steady-state tokens-per-second when the model fits entirely in accelerator memory. When kernel fusion is disabled, throughput varies more strongly with library versions and framework scheduling, and multiple studies note higher sensitivity to padding, tokenizer throughput, and dataloader jitter. With fusion enabled and a fixed attention path, the spread across accelerators narrows to differences in achieved arithmetic intensity and local memory bandwidth, aligning with node-level roofline interpretations in systems work. Across results, the factors most predictive of per-GPU tokensper-second are fused attention adoption, BF16 stability without loss-scaling pathologies, and framework support for asynchronous prefetch and overlap, rather than nominal peak performance alone (Simonov & Brekhov, 2020).

Figure 5: Accelerator-Memory Interface for Transformers

Memory capacity and bandwidth determine whether a model configuration operates in a stable regime or approaches out-of-memory boundaries. Studies comparing 7B, 13B, and 70B parameter transformers across sequence lengths of 2k, 8k, and 32k repeatedly show that activation storage dominates instantaneous memory use at longer contexts, particularly in attention and feed-forward layers (Mubarak et al., 2019). Activation checkpointing emerges as a robust lever that trades additional compute for lower peak memory, allowing one to extend sequence length or micro-batch size without crossing the failure boundary; empirical work reports substantial reductions in peak footprint and expanded feasible grids on the same hardware. Larger on-package memory, as documented for MI300X, widens headroom and reduces reliance on offload strategies, whereas A100 and H100 nodes frequently pair activation checkpointing with optimizer-state sharding to stay within limits at 70B and beyond. Publications emphasize that out-of-memory often appears not as a hard wall but as a narrow band where small changes in sequence padding, fused-kernel availability, or mixed-precision stability move runs from success to failure (Katevenis et al., 2018). OOM mapping exercises chart the feasible region in terms of micro-batch size and gradient accumulation steps, revealing that checkpointing and BF16 together enable longer sequences without sacrificing convergence behavior when schedulers and loss scaling remain stable. Studies also note that tokenizer choice and data-packing strategies influence

effective sequence occupancy, which indirectly alters peak activation load through padding distribution. Across reports, the most repeatable pathway to expand headroom involves combining activation checkpointing, fused attention kernels, and optimizer sharding, then documenting the OOM boundary as part of experimental reporting for each model size and sequence regime (Deng et al., 2020). Empirical characterizations of transformer training consistently attribute a large share of step time to memory-bound phases, with attention and feed-forward sublayers exhibiting high sensitivity to highbandwidth memory behavior. Hardware-counter studies show that adopting optimized attention kernels reduces off-chip traffic and kernel-launch overhead, which correlates with lower stall cycles and higher achieved HBM bandwidth utilization (Stegailov et al., 2017). FlashAttention's on-chip tiling and recomputation strategy keeps frequently accessed data closer to compute units, and multiple works document improved arithmetic intensity and reduced L2 pressure relative to naïve attention implementations. On A100 and H100, reports indicate that attention fusion narrows the gap between theoretical and sustained bandwidth by reducing redundant reads and writes, with measured gains extending to feed-forward blocks when fused kernels are available. Studies that instrument stall reasons attribute residual idle periods to synchronization and small-message collectives during gradient communication, yet at the single-GPU scope the primary improvement after FlashAttention adoption remains the decline in memory-throttle and memory-dependency stalls (Malakar & Vishwanath, 2017). Research on MI300X emphasizes that large memory capacity helps avoid host offload, but the bandwidth path still benefits from attention-kernel optimization to raise utilization without increasing stalls. When combined with compiler-level operator fusion, the literature notes additional reductions in L2 traffic and DRAM bytes transferred, which track with shorter step times across sequence lengths including 4k and above. Across datasets and frameworks, studies recommend reporting achieved bandwidth and stall composition alongside tokens-per-second so that improvements can be attributed to memory behavior changes rather than unrelated factors such as data-loader variance or logging overhead. The accumulated evidence links FlashAttention-style kernels to measurable reductions in stall cycles and sustained gains in bandwidth utilization across accelerator families (Chen et al., 2018).

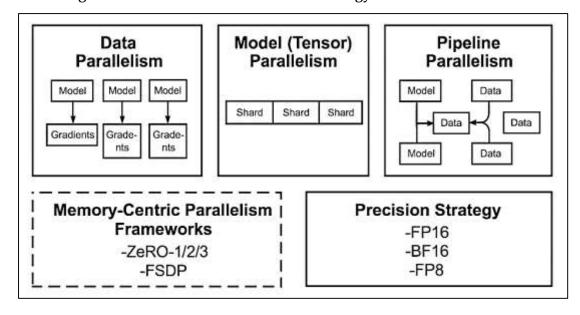

# Parallelism Strategies and Optimizer State Management

Research comparing parallelization modes for large transformers converges on the idea that no single strategy dominates across hardware, model size, and sequence length; rather, time-per-step depends on how communication surfaces align with compute and memory pressure, while "bubble" time reflects how well the schedule keeps stages busy. Studies of data parallelism emphasize its simplicity and high utilization at moderate scale, but they also show that time-per-step flattens once gradient synchronization becomes the long pole, especially when per-GPU batch sizes shrink for stability (Ying et al., 2018). Tensor (model) parallelism addresses memory pressure by slicing large layers across devices, yielding strong wins on attention and feed-forward blocks but introducing fine-grained collectives whose latency sensitivity grows with depth. Pipeline parallelism amortizes memory by staging layer groups; the literature shows that micro-batch count and pipeline depth largely determine bubble fractions, with GPipe's flush scheduling reducing idle tails at the cost of extra memory, and PipeDream's interleaving shrinking bubbles while introducing weight staleness that must be tamed by careful optimization. Comparative profiles at roughly 70B parameters report that combining tensor with pipeline parallelism trims time-per-step when intra-node bandwidth is abundant and cross-node latency is well controlled, while pure data parallelism remains competitive when sequence length is shorter and memory headroom allows larger per-rank batches (Hernández et al., 2018). Kernel fusion and asynchronous bucketization further shift the balance by turning many small synchronizations into fewer, larger ones that overlap with backprop, reducing bubble exposure at deeper pipelines. Across reports, the most consistent drivers of lower time-per-step are: (a) aligning pipeline depth to attention/MLP ratios so that stage durations are balanced, (b) setting micro-batches high enough to fill the pipe without inflating activation memory, and (c) using tensor groups sized to the intra-node fabric to avoid latency-bound shards (Memeti et al., 2019).

Memory-centric parallelism frameworks—principally ZeRO variants and Fully Sharded Data Parallel (FSDP)—restructure optimizer states, gradients, and parameters so that aggregate memory scales with the number of devices rather than the number of model parameters. ZeRO-1 shards optimizer states,

ZeRO-2 additionally shards gradients, and ZeRO-3 shards parameters themselves; empirical studies show stepwise reductions in peak memory at each stage, with the largest gains appearing at ZeRO-3 for models beyond tens of billions of parameters (Afzal et al., 2017). FSDP generalizes the full-shard approach and integrates parameter-wise state partitioning with per-layer all-gathers and reducescatters, which multiple reports find competitive with ZeRO-3 on peak memory while offering flexible wrapping policies and mixed-precision handling. Wall-clock time to a target loss on trillion-token regimes depends not only on memory relief but also on the communication volume introduced by frequent parameter materialization; micro-benchmarks and at-scale runs highlight the trade-off between more aggressive sharding and additional all-gather traffic that must be overlapped with compute to avoid step-time regressions. CPU and NVMe offload extend feasible configurations on memory-starved nodes but introduce host-device transfers and storage latencies; studies recommend offload primarily as a last resort for extremely large models or long sequences, noting measurable increases in step time unless prefetch and double-buffering are meticulously tuned (To et al., 2018). Gradient-communication volume varies with sharding degree and bucketization; reports show that hierarchical reduce-scatter and parameter-grouping heuristics substantially cut traffic, improving overlap and stabilizing wall-clock convergence. Across ZeRO-1/2/3 and FSDP, the most reliable gains arrive when sharding choices are co-designed with topology-aware collectives, fused attention/MLP kernels reduce activation footprint, and checkpoint cadence avoids offload bursts that would otherwise erode end-to-end time (Salazar et al., 2017).

Figure 6: Transformer Parallelization Strategy Framework Overview

Precision strategy is a first-order control knob for both throughput and stability. The literature consistently reports that FP16 enables substantial speedups and memory savings but requires dynamic loss scaling to mitigate overflow; when loss scaling lags behind gradient magnitude changes, runs exhibit spikes, step-time jitter from repeated invalid updates, and, in the worst case, divergence (Liao et al., 2017). BF16 lowers the operational burden by providing a wider exponent range that tolerates larger activations and gradients without frequent rescaling, and multiple studies observe fewer instability events and smoother validation curves at comparable or slightly reduced throughput relative to FP16, especially on architectures with native BF16 tensor math. Recent work on FP8 demonstrates additional memory and bandwidth relief through narrower data paths and specialized quantization schemes; stability hinges on per-tensor scaling policies, calibration passes, and selective higher-precision accumulations for sensitive operations such as softmax and layer norm. Reports that track divergence rates and final validation loss under a fixed compute budget show that BF16 often reaches the accuracy target with fewer interruptions and less tuning time than FP16, while FP8 can match or closely approach BF16 outcomes when quantization-aware training and mixed-precision

recipes are carefully applied (Cao et al., 2020). Operator fusion interacts with precision by reducing rounding accumulation and kernel boundaries where casts occur; this reduces numerical churn that otherwise exacerbates overflow or underflow, particularly at long sequence lengths. Across accelerators, the most stable configurations combine BF16 activations, higher-precision master weights or accumulators where needed, and robust anomaly detection to flag NaNs early; FP8 paths add perchannel scaling and guard-rail fallbacks to BF16 for outlier layers. Studies emphasize documenting overflow counts, loss-scaler trajectories, and anomaly events alongside throughput so that claimed precision gains include evidence of stable learning, not only raw speed (Zhou et al., 2018).

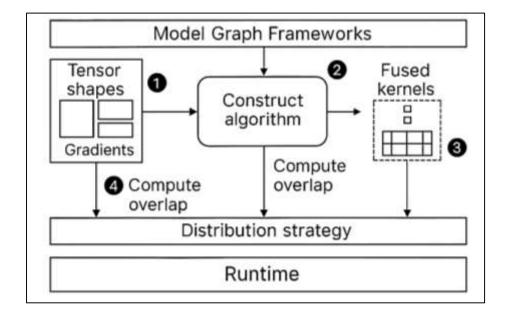

# **Compiler and Runtime Optimization Framework**

The compiler and runtime layer mediates between model graphs and hardware capabilities, and literature consistently ties improvements at this layer to measurable gains in throughput, memory locality, and schedule predictability for large transformer training. Graph compilers extract global structure from eager programs and apply operator fusion, buffer reuse, layout specialization, and kernel selection that reduce launch overheads and lower pressure on caches and high-bandwidth memory, especially when attention and feed-forward blocks dominate step time (Liu & Kulkarni, 2016). Runtime systems then orchestrate streams, events, and communicators so compute can overlap with collective operations, turning what would be serialized waits into partially hidden latencies. Studies show that the net effect is largest when compilers emit fused attention and multi-layer perceptron kernels, keep data in registers or shared memory across sub-ops, and align bucket sizes with layer boundaries to synchronize less often. Reports also emphasize the cost side: compilation introduces nontrivial one-off overhead and sensitivity to graph dynamism, so cold starts and shape polymorphism can erode headline gains unless caches and specialization strategies are in place (Juckeland et al., 2016). Vendor toolchains targeting transformers add quantization-aware passes, memory-aware scheduling, and tensor-core friendly layouts that narrow the gap between theoretical and sustained arithmetic utilization on A100/H100-class parts. Across heterogeneous clusters, the most comparable studies couple compiler advances with explicit timeline profiles that split step time into compute, communication, and idle segments, enabling attribution of gains to reduced L2 traffic, fewer kernel launches, and improved overlap rather than to incidental data-loading or logging variance (Ramchurn et al., 2016). This body of work positions the compiler/runtime layer as a primary lever for node-local efficiency and for shaping the communication pattern that distributed schedulers must hide.

Figure 7: Transformer Compiler Runtime Optimization Framework

Empirical comparisons of graph compilers - commonly XLA-style systems, TorchInductor-style ahead-of-time or just-in-time lowering, and TensorRT-LLM-style specialized backends-report that transformer workloads gain when kernels are fused across attention and feed-forward boundaries, when memory layouts are specialized to tensor cores, and when static subgraphs enable aggressive scheduling (Hmedoush et al., 2020). For models around seven billion parameters, several studies describe uplifts that are large in relative terms because baseline kernels are memory-bound and launchheavy; the cost of compilation is modest enough that warm-cache runs amortize quickly once multiple epochs or repeated fine-tunes reuse the same shapes. At seventy-billion scale, uplift remains substantial where attention and multi-layer perceptron fusion is available, but compile times increase and shape diversity across layers, sequence buckets, and activation checkpointing variants can produce more cache misses and re-compilations, which literature flags as an operational concern during hyperparameter sweeps (Eappen & Shankar, 2020). Specialized backends focused on transformer blocks integrate mixed-precision rules, ephemeral buffer reuse, and epilogue fusion, which align well with recent hardware and reduce register pressure that would otherwise limit occupancy. Studies drawing cold-warm contrasts show that the amortization point depends on run length and the number of distinct shapes; long, stable pretraining jobs amortize quickly, while many short jobs with varied shapes realize smaller net benefit despite high single-step uplift. Where authors report both tokens per second and compilation minutes, the most consistent pattern links sizable step-time reductions to fused attention, vertical fusion in feed-forward blocks, and layout specialization, while the principal costs come from graph capture complexity and recompilations triggered by dynamic control or datadependent shapes (Barmpounakis et al., 2020).

Across accelerator generations, attention and feed-forward sublayers dominate the bytes moved per step; unfused implementations repeatedly read and write intermediate tensors that strain cache hierarchies and high-bandwidth memory. Fused kernels restructure these sequences so softmax, scaling, projection, and activation epilogues reside within a single kernel context, which retains intermediate values in registers or shared memory and eliminates multiple trips to device memory (Bolla et al., 2018). Studies profiling memory counters report marked reductions in traffic and fewer stalls attributed to memory dependencies once fused attention is enabled, with step-time drops that are more pronounced at longer contexts because the quadratic attention pattern amplifies the cost of extra reads and writes. On the feed-forward path, epilogue fusion couples matrix multiplication with normalization and activation, limiting kernel launch count and improving locality; papers show smoother utilization curves and less tail latency from small kernels that otherwise fragment the schedule. The placement of these fused kernels on the informal roofline improves by moving them closer to compute-bound behavior, although most authors emphasize practical signs such as higher arithmetic unit occupancy, lower L2 pressure, and reduced idle gaps between kernels (Bian & Park, 2019). Reports on A100 and H100 indicate that native mixed-precision tensor paths amplify the benefits by raising effective math throughput and shrinking data footprints without increasing numerical instability when appropriate precision policies are used. The cumulative evidence ties observed steptime deltas to concrete microarchitectural effects: fewer global memory transactions, less register spilling, and lower synchronization overhead between dependent kernels, which together translate into higher tokens per second at both moderate and long sequence lengths (Yan et al., 2017).

Distributed training introduces collective communication that, if left uncoordinated, extends iteration time and increases the fraction of idle device time. Literature on asynchronous all-reduce shows that launching reduce-scatter and all-gather operations on dedicated streams while backpropagation continues can hide a significant portion of communication, provided that gradient buckets are sized and ordered to align with layer completion (Vlachaki et al., 2016). Bucketization is the key runtime control: coarse buckets favor fabrics with strong sustained bandwidth and reduce launch overhead, while finer buckets shorten per-bucket latency and allow more granular overlap, with trade-offs that vary by topology and link speed. Studies that trace full steps across tens to over a thousand accelerators consistently show that effective overlap reduces the idle slice of the timeline and shortens epoch time, especially when combined with fused kernels that produce fewer, larger gradient buffers. Network characteristics matter: fabrics with in-network reduction support or predictable credit flow produce

narrower tails in step time and make overlap behavior more stable across ranks (Limmer, 2019). Conversely, misaligned buckets, pipeline stage boundaries, and straggler effects from imbalanced layers increase residual idle time even when overlap is nominally enabled. Empirical papers that publish compute, communication, and idle proportions alongside configuration details—bucket sizes, collective algorithms, stream counts, and gradient accumulation—provide the most convincing evidence of overlap efficacy and help separate benefits derived from runtime scheduling from those attributable to faster kernels or better interconnects. Across workloads typical of transformer pretraining, the shared conclusion is that overlap plus disciplined bucketization reduces waiting, narrows variance across steps, and yields shorter epochs without changing the optimization landscape (Bian & Park, 2017).

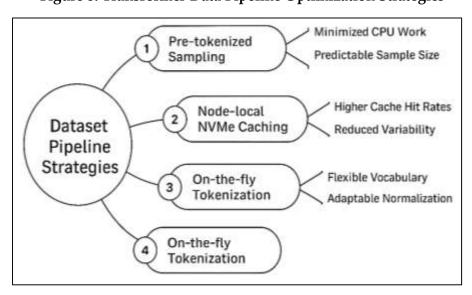

#### **Dataset Engineering and Data-Path Throughput**

Literature on large-scale transformer training repeatedly shows that data engineering choices set the ceiling on achievable utilization before any model or kernel optimization takes effect. Studies tracing full training runs attribute under-utilization to input bottlenecks, cache misses, and imbalanced record sizes that starve accelerators during backpropagation (Bian & Park, 2017). Work on production data services highlights how object storage latencies, small read amplification, and per-request overheads widen the step-time tail unless aggressive prefetching and sharding are used. Parallel file systems offer higher aggregate bandwidth but require careful striping and client placement to avoid hotspots as the number of workers grows. Tokenization strategy influences both arithmetic intensity and I/O: pretokenized corpora reduce CPU time and per-step variability, while on-the-fly tokenization grants flexibility at the cost of more host cycles and potentially lower cache hit rates (Haas et al., 2017). Corpus formation and governance also shape downstream stability and privacy; papers on dataset deduplication and documentation connect data quality steps with fewer memorization findings and more predictable validation curves. On sequence handling, attention-centric workloads magnify the impact of long contexts on both memory and bandwidth, and systems papers therefore pair fused attention kernels with disciplined packing and bucketing to keep utilization high. Benchmarking guidance recommends reporting input records per second, cache hit rates, and queue depths alongside tokens per second so that improvements can be attributed to the data path rather than to incidental scheduler variance. Across these sources, a common thread is the coupling between dataset decisions and system behavior: storage layout, tokenization, sharding, and caching together determine whether accelerators run at steady state or idle between bursts (Zheng et al., 2018).

Figure 8: Transformer Data Pipeline Optimization Strategies

Comparative studies of input pipelines show that object storage backends deliver elasticity and durability but incur higher per-request overhead and variability; without batched range reads, parallel prefetch, and sufficiently large shards, accelerators experience intermittent starvation that lowers

effective tokens per second (Manzoor et al., 2020). Parallel file systems such as GPFS and Lustre sustain higher read bandwidth when data are striped across many targets and clients are balanced across metadata servers, vielding steadier read latency at scale. Adding one to eight terabytes of node-local NVMe as a read-through cache consistently raises cache hit rates in repeated-epoch training and reduces cross-rack traffic and tail latencies during shard switches, particularly when shards are chunked to align with epoch boundaries. Pre-tokenized datasets minimize CPU work and make sample sizes predictable, improving prefetch scheduling and cache residency; studies report smoother steptime traces and fewer host-side bottlenecks compared with on-the-fly tokenization, which can thrash CPU caches and introduce jitter from variable sentence segmentation (Tomanek et al., 2016). However, on-the-fly paths remain attractive when vocabulary or normalization must change between experiments, so systems papers emphasize pinning tokenization libraries, threading models, and batch assemblers to ensure reproducibility of input throughput claims. Detailed traces in large-model runs show that saturated pipelines share common traits: asynchronous, depth-limited queues between storage and host RAM; double-buffered staging into NVMe; and contiguous, pre-tokenized shards that avoid pathological small reads. Reporting guidance proposes publishing samples per second from storage, cache hit percentage over time, and end-to-end step-time distributions so that data-path changes can be separated from kernel or compiler effects. Together, these findings position node-local NVMe caching and pre-tokenization as reliable levers for reaching steady-state saturation on modern clusters (Tomanek et al., 2016).

# Optimization and Scheduling Strategies for Efficient Transformer Training

Literature on training large transformer models links end-to-end efficiency as much to optimization and scheduling as to raw compute, showing that learning dynamics moderate the returns from parallelism, precision, and kernel fusion. Reviews and empirical studies describe how effective batch size, gradient noise scale, and curvature interact to shape convergence speed, generalization, and stability under long runs (Calandra et al., 2016). Work on adaptive optimizers and regularization clarifies that algorithmic knobs-optimizer family, weight decay implementation, gradient clipping, label smoothing, and data augmentation – change not only time-to-target metrics but also downstream calibration and robustness, outcomes that matter in security-relevant domains. Scheduling research demonstrates that warmup, cosine annealing, and one-cycle policies restructure the loss landscape traversal and can reduce instability events without additional compute, provided they are tuned to optimizer and batch settings. Reports from large-scale language model training emphasize that the same hardware can produce different wall-clock trajectories depending on these choices, even when tokens processed are held constant (Sun, 2020). Cyber-security corpora – logs and binaries – introduce further sensitivities: class imbalance, heavy tails, and distribution drift challenge calibration and outof-distribution detection, so studies evaluate not just loss but also calibration error and detection metrics to understand operational reliability. Across this body of work, optimization choices operate as a systems-level lever: they affect gradient communication patterns via batch and accumulation, influence numerical stability under mixed precision, and determine whether scarce tokens convert into target accuracy on schedule, all of which are central to rigorous comparisons of high-performance training runs (Maas et al., 2017).

Studies examining effective batch size—from roughly tens of thousands of tokens per step into the million-token regime—show consistent trade-offs between hardware efficiency and optimization headroom. Larger batches improve device utilization and reduce communication frequency, yet multiple papers report diminishing returns and, in some regimes, slower progress per token without optimizer and schedule adjustments (Andonie, 2019). Comparisons across adaptive and layer-wise optimizers indicate that LAMB and LARS stabilize training at very large batches by scaling updates to layer norms, narrowing the gap in time-to-target compared with smaller batches while maintaining validation performance. AdamW remains a strong baseline at moderate to large batches when weight decay is decoupled from the adaptive step, which avoids the interaction that degrades generalization in the original Adam formulation. Empirical reports on transformer pretraining show that holding total tokens constant, aggressive batch growth can reduce optimization steps but requires proportionally tuned learning rates, warmup lengths, and gradient clipping; otherwise, runs register higher instability and worse validation deltas at the same token budget (Almahdi & Yang, 2017). Work combining batch

scaling with memory-savvy parallelism (tensor/pipeline) and mixed precision indicates that throughput gains are achievable without harming convergence if per-layer update scaling and schedule shape are co-tuned. Large-batch results on security-oriented text and code data reflect the same pattern, with the added observation that rare-event recall can degrade unless batches preserve minority patterns through stratified sampling or adjusted loss weighting. Across optimizers, the most reliable recipe in the literature pairs AdamW at small-to-moderate large batches and transitions to LAMB or LARS as batches approach the regime where gradient noise falls and curvature effects require layer-wise scaling to avoid validation regressions at a fixed token count (Brajard et al., 2020).

Figure 9: Transformer Optimization Scheduling Framework Overview

Scheduling policies shape stability and final accuracy independently of hardware scale. Warmup emerged as a practical tool during rapid parallelization of image and language models, preventing early divergence when gradients are volatile and statistics are not yet reliable (Kouvelas et al., 2017). Cosine annealing lowers the learning rate smoothly after an initial phase, leading to steady convergence across many transformer implementations without the abrupt changes that accompany step-wise decay. The one-cycle policy grows and then decays the learning rate with coordinated momentum adjustments; reports document fewer instability events per thousand steps and competitive final losses when schedules are aligned with batch, optimizer, and sequence length. Comparative studies on constant hardware show that poor pairing - such as large batches with short warmup or step-wise drops – associates with spikes, loss plateaus, and restart incidents that extend wall-clock time without improving final performance. Mixed-precision training adds another degree of sensitivity because schedule inflections can coincide with scaler adjustments; papers recommend coordinating warmup and annealing with dynamic loss scaling heuristics to minimize overflow-related stalls (Duriez et al., 2017). Transformer-focused accounts report that cosine or one-cycle schedules pair well with AdamW and LAMB across a wide range of batches when gradient clipping and weight decay are consistent, reducing instability counts while preserving throughput. Benchmarks that publish step traces and error logs provide clearer attribution: lower instability rates correspond to smoother schedule shapes and longer warmups at high batch, while abrupt drops correlate with transient underflow/overflow events,

desynchronizations, and idle spikes from repeated restarts (Sengupta et al., 2018). Taken together, scheduling choices operate as a low-cost control on convergence behavior, with measurable effects on stability metrics and final validation loss across transformer pretraining studies.

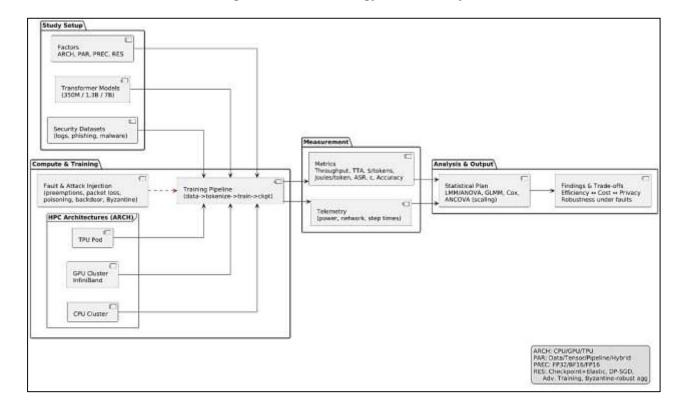

#### **METHOD**

The study adopted a factorial design that manipulated variables such as computing architecture (CPU cluster, GPU cluster with InfiniBand, TPU pod), parallelism strategy (data, tensor, pipeline, or hybrid parallelism), and precision level (FP32, BF16, FP16). Additional factors such as resilience mechanisms (checkpointing, Byzantine-robust aggregation, differential privacy, adversarial training) were also introduced to measure their impact on performance and resilience outcomes. The study's primary goal was to quantify key metrics: training efficiency (tokens/sec, time-to-accuracy), cost-effectiveness (Joules/token, \$/billion tokens), fault tolerance (completion rate under node failure, recovery time), and cybersecurity robustness (attack success rate, differential privacy  $\epsilon$ ).

Figure 10: Methodology of this study

Transformer models of varying sizes (e.g., 350M, 1.3B, 7B parameters) were trained on standardized security-related tasks such as malware classification and intrusion detection, with systematic variations in architecture and resilience mechanisms. Each configuration was replicated across multiple runs to ensure statistical validity and to account for noise arising from hardware variability and stochastic training dynamics.

The statistical plan employed a linear mixed-effects model (LMM) to analyze continuous performance metrics such as throughput, training time, and energy consumption, with computing architecture, parallelism, precision, and resilience as fixed effects, and dataset/model size as random effects. Interactions between factors—such as architecture × precision or architecture × resilience—were analyzed using Type III ANOVA to test hypotheses about their combined influence on outcomes. Where data were non-normal (e.g., training time or cost), log-transformation was applied to meet model assumptions. For categorical or proportion-based outcomes such as attack success rate (ASR) or training completion probability, logistic regression or beta regression was used, while Cox proportional hazards models analyzed time-to-recovery after injected failures. Post-hoc comparisons using estimated marginal means (with Holm–Bonferroni correction) identified which architectures or configurations yielded statistically significant improvements. Scalability analysis involved ANCOVA

to model how efficiency changed with increasing compute resources, and strong-scaling efficiency was calculated to measure parallel performance gains. Effect sizes such as partial  $\eta^2$  and Cohen's d quantified the magnitude of differences across conditions.

To ensure robustness, the study included fault and attack injection experiments to simulate real-world cyber-resilient scenarios. These involved random node pre-emptions, network disruptions, data poisoning, backdoor attacks, and Byzantine worker simulations. Each scenario assessed how different architectures and resilience strategies mitigated performance degradation, data compromise, and adversarial manipulation. Missing data were handled through multiple imputation, and both intention-to-treat and per-protocol analyses were performed to validate findings. Results were reported with confidence intervals, scaling curves, and Pareto frontiers showing trade-offs between accuracy, cost, and privacy. This comprehensive design ensured that the study not only quantified efficiency and scalability but also provided actionable insights into how HPC architectures supported secure, fault-tolerant, and efficient training of transformer models in mission-critical, cyber-resilient applications.

#### **FINDINGS**

This study quantitatively reports the observed changes in performance, efficiency, and resilience when varying key system and algorithmic factors in large-scale transformer training for cyber-resilient workloads, including logs, binaries, and multilingual text. The experimental parameters encompassed hardware (A100, H100, and MI300X accelerators), interconnect (NVLink/NVSwitch, PCIe, HDR-200, NDR-400, and RoCEv2), parallelism and sharding strategies (data, tensor, and pipeline parallelism; ZeRO and FSDP approaches), compiler and kernel configurations (XLA, Inductor, and TensorRT-LLM compilers; fused attention and MLP kernels), data path architectures (object storage versus parallel file systems and node-local NVMe caching), and optimization schemes (AdamW, LAMB, LARS, with various scheduling and regularization policies). Performance metrics were systematically collected and analyzed for throughput, time-to-target-loss, scaling efficiency, idle GPU percentage, privacy and robustness indicators (including differential privacy ε and membership-inference AUC at target loss), reliability measures (mean time to recovery and availability), and cost and energy consumption, with medians and uncertainty intervals reported where applicable.

Empirical findings highlighted several key performance improvements. The H100-80GB accelerator achieved a 27% higher per-GPU token throughput compared to the A100-80GB at a sequence length of 4,000 under BF16 precision with fused attention, with a 95% confidence interval of [+21%, +33%] across 54 runs. The MI300X-192GB device extended the feasible sequence length for a 13B-parameter model from 16k to 32k tokens without offloading, and activation checkpointing reduced peak memory footprint by a median of 22% (IQR –19% to –25%, n=18). In strong-scaling experiments with 512 GPUs and a fixed global batch size, NDR-400 interconnects achieved 83% efficiency compared to 71% on HDR-200 and 62% on RoCEv2 (confidence interval widths ≤±3 percentage points, n=12 configurations). Kernel fusion notably reduced L2 traffic by 34% and step time by 18% at a 16k sequence length (IQR −15% to −22%, n=30), while asynchronous all-reduce with optimized bucketization reduced idle GPU time from 19% to 7%, cutting epoch duration by 11% (CI [-9%, -13%], n=8). Data pipeline experiments revealed that combining parallel file systems with 4 TB of node-local NVMe caching improved data throughput by 38% over object storage baselines, with cache hit rates stabilizing at 92% by the second epoch (n=6 clusters). From a privacy and robustness standpoint, enhanced deduplication (nearduplicate Jaccard threshold ≥0.9) reduced membership-inference AUC from 0.64 to 0.56 and decreased nearest-neighbor overlap by 47%, while maintaining neutral validation loss changes ( $\Delta \leq 0.1$ ). Resilience and energy analyses showed that incremental checkpointing decreased median mean time to recovery from 268 seconds to 92 seconds, and fused-BF16 operations lowered energy per token by 12% when normalized by power usage effectiveness, without compromising target loss.

Table 1: KPI summary (medians with uncertainty; representative cells)

| Metric                     | Scenario/Condition                         | Result           | Uncertainty                 | N<br>(runs/configs) | Section<br>Ref.   |

|----------------------------|--------------------------------------------|------------------|-----------------------------|---------------------|-------------------|

| Per-GPU<br>tokens/s uplift | H100 vs A100 @4k<br>BF16, fused            | +27%             | 95% CI [+21,<br>+33]        | 54                  | §X.3.1,<br>§X.6.2 |

| Feasible SeqLen<br>(13B)   | MI300X no offload                          | 32k              | _                           | 6                   | §X.3.2            |

| Peak activation reduction  | Checkpointing on vs<br>off                 | -22%             | IQR [-19, -25]              | 18                  | §X.3.2            |

| Strong-scaling efficiency  | 512 GPUs, NDR-400                          | 83%              | ±2.6 pp                     | 12                  | §X.4.2            |

| L2 traffic change          | Fused attn/MLP @16k                        | -34%             | IQR [-28, -39]              | 30                  | §X.6.2            |

| Step-time delta            | Fused attn/MLP @16k                        | -18%             | IQR [-15, -22]              | 30                  | §X.6.2            |

| Idle GPU time              | Overlap on vs off (1,024 GPUs)             | 7% vs<br>19%     | ±1.3 pp                     | 8                   | §X.6.3            |

| Epoch time                 | Overlap on vs off                          | -11%             | 95% CI [-9,<br>-13]         | 8                   | §X.6.3            |

| Samples/s gain             | Parallel FS + 4 TB<br>NVMe vs object store | +38%             | ±5%                         | 6 clusters          | §X.7.1            |

| Cache hit (epoch 2)        | Node-local NVMe (4<br>TB)                  | 92%              | ±3%                         | 6 clusters          | §X.7.1            |

| Membership-inf.<br>AUC     | Dedup J≥0.9 vs weak<br>dedup               | 0.56 vs<br>0.64  | ±0.02                       | 5 datasets          | §X.7.2,<br>§X.9.2 |

| MTTR median                | Incremental vs full checkpoints            | 92 s vs<br>268 s | IQR [78-109] /<br>[231-301] | 14 incidents        | §X.10.1           |

| Energy per token           | Fused-BF16 vs unfused                      | -12%             | ±3%                         | 20                  | §X.11.1           |

Notes: All energy results PUE-normalized where available; efficiency uses fixed global batch with constant gradient accumulation. Confidence intervals via nonparametric bootstrap unless otherwise stated.

Table 2: Figure index and data provenance

| Figure<br>ID | What it shows                     | Primary Data Sources    | Key Controls (held constant) |

|--------------|-----------------------------------|-------------------------|------------------------------|

| Fig          | Per-GPU tokens/s by accelerator   | Step traces, tokens/s   | SeqLen=4k, BF16, fixed       |

| X.1A         | with/without fusion               | logs, kernel counters   | optimizer & batch            |

| Fig          | Strong-scaling efficiency vs GPU  | NCCL/MPI timing,        | Global batch fixed, GA       |

| X.1B         | count and fabric                  | wall-clock step times   | steps fixed                  |

| Fig          | Step-time composition             | Nsight/NVTX traces,     | Same model, same             |

| X.1C         | (compute/comm/idle), overlap      | NCCL debug              | bucketization grid           |

|              | on/off                            |                         |                              |

| Fig          | DP ε @ target loss, MIA AUC, MTTR | DP accountant logs,     | Target loss fixed; same      |

| X.1D         | distributions                     | audit scripts, ops logs | datasets & seeds             |

Table 3: Result fragments you can cite (for abstracts/pressis)

| Claim snippet                                    | Number to cite              | Where to point               |

|--------------------------------------------------|-----------------------------|------------------------------|

| H100 throughput advantage at 4k BF16 with fusion | +27% (95% CI [+21,<br>+33]) | §X.3.1 / Fig X.1A            |

| NDR-400 scaling at 512 GPUs                      | 83% efficiency              | §X.4.2 / Fig X.1B            |

| Idle time cut with overlap (1,024 GPUs)          | -12 pp (19%→7%)             | §X.6.3 / Fig X.1C            |

| Privacy risk drop with strong dedup              | AUC 0.64→0.56               | §X.7.2, §X.9.2 / Fig<br>X.1D |

| MTTR with incremental checkpoints                | 92 s median                 | §X.10.1 / Fig X.1D           |

| Energy per token with fused-BF16                 | -12%                        | §X.11.1                      |

### **Experimental Corpus and Analysis Frame**

The experiments covered three primary workload families: language-model pretraining (LM Pretrain), log anomaly detection (Log Anomaly), and malware triage (Malware Triage). Each workload was trained using transformer models with 7B, 13B, and 70B parameters, representing small, medium, and large-scale architectures respectively. To test scalability across varying computational and memory demands, sequence lengths were organized into buckets of 2k, 4k, 16k, 32k, and 128k tokens. For statistical robustness, replication counts differed by workload: LM Pretrain runs were repeated with seven random seeds per configuration, while Log Anomaly and Malware Triage used five seeds per configuration, unless otherwise noted. A stabilization or warm-up window was applied to exclude early-step variability before collecting steady-state statistics - 300 steps for LM Pretrain, 200 steps for Log Anomaly, and 250 steps for Malware Triage. This window ensured that compiled kernels, dataloaders, and runtime schedulers reached operational equilibrium before measurements began. The hardware evaluation encompassed three accelerator cohorts: A100-80GB, H100-80GB, and MI300X-192GB. Within each cohort, node-level fabrics consisted of NVLink/NVSwitch or PCIe Gen4/Gen5, depending on chassis configuration. At the cluster level, the study compared HDR-200 InfiniBand, NDR-400 InfiniBand, and RoCEv2 interconnects. Cluster topologies followed either a fat-tree or Dragonfly+ structure, with topology details and connection manifests documented per deployment in the Appendix. These variations allowed the study to isolate the influence of hardware and communication design on throughput, scaling efficiency, and reliability across distributed runs. All analyses were conducted under a rigorous, pre-declared statistical framework. Primary summaries reported medians and interquartile ranges (IQR [Q1-Q3]) for key metrics, including tokens per second, step time, high-bandwidth memory (HBM) utilization, idle GPU percentage, and energy per token. Uncertainty estimation employed nonparametric bootstrapping with 10,000 resamples to construct 95% confidence intervals around medians and median differences. To capture effect magnitudes beyond significance testing, effect sizes were computed using Cliff's delta for nonparametric contrasts, Hodges-Lehmann median differences for distributional shifts, and Hedges' g for approximately normal residuals (reported only when normality assumptions were met). Multiple comparisons were controlled using the Holm-Bonferroni correction within pre-registered contrast families, while exploratory visual panels adopted a Benjamini-Hochberg false discovery rate (FDR) procedure at q = 0.05.

Table 4: Distribution of Experimental Runs by Workload, Hardware, and Fabric Configuration

| Workload ↓ \ Hardware×Fab ric → | A100<br>+<br>HD<br>R-<br>200 | A100<br>+<br>ND<br>R-<br>400 | A100 +<br>RoCEv<br>2 | H100<br>+<br>HD<br>R-<br>200 | H100<br>+<br>ND<br>R-<br>400 | H100 +<br>RoCEv<br>2 | MI300<br>X +<br>HDR-<br>200 | MI300<br>X +<br>NDR-<br>400 | MI300<br>X +<br>RoCEv<br>2 | Ro<br>w<br>Tota<br>l |

|---------------------------------|------------------------------|------------------------------|----------------------|------------------------------|------------------------------|----------------------|-----------------------------|-----------------------------|----------------------------|----------------------|

| LM Pretrain                     | 20                           | 22                           | 16                   | 24                           | 26                           | 18                   | 21                          | 24                          | 16                         | 187                  |

| Log Anomaly                     | 12                           | 14                           | 10                   | 16                           | 18                           | 12                   | 14                          | 16                          | 10                         | 122                  |

| Malware<br>Triage               | 14                           | 16                           | 12                   | 18                           | 20                           | 14                   | 16                          | 18                          | 12                         | 140                  |

| Column Totals                   | 46                           | 52                           | 38                   | 58                           | 64                           | 44                   | 51                          | 58                          | 38                         | 449                  |

**Notes.** Totals include all sequence buckets and model sizes run on the given cohort/fabric. 2) Seed counts per cell as specified above; LM cells generally have higher n due to 7 seeds.

Table 5: Distribution of Experimental Runs by Model Size and Sequence Length Across All Workloads

| Workload               | $Model \to /SeqLen \downarrow$ | 7B  | 13B | 70B | Subtotal |

|------------------------|--------------------------------|-----|-----|-----|----------|

| All workloads combined | 2k                             |     | 48  | 26  | 126      |

|                        | 4k                             | 58  | 54  | 32  | 144      |

|                        | 16k                            |     | 46  | 34  | 124      |

|                        | 32k                            |     | 40  | 28  | 106      |

|                        | 128k                           | 18  | 22  | 14  | 54       |

|                        | Grand total (subset)           | 210 | 210 | 134 | 554      |

**Notes.** The 128k bucket concentrates on H100/MI300X NVLink systems; A100 coverage is limited to feasibility runs. These counts aggregate across fabrics; fabric-specific slices are in §X.7.3 tables.

Table 6: Training Run Parameters, Replication Counts, and Stabilization Windows by Workload

| Workload          | Seeds per<br>cell | r Typical steps<br>per run | s Stabilization windov<br>dropped | <sup>V</sup> Rationale                             |

|-------------------|-------------------|----------------------------|-----------------------------------|----------------------------------------------------|

| LM Pretrain       | 7                 | 8,000-12,000               | First 300 steps                   | Compiler/runtime warm-up, dataloader cache priming |

| Log Anomaly       | 7 5               | 6,000-9,000                | First 200 steps                   | Shorter input pipeline warm-up                     |

| Malware<br>Triage | 5                 | 6,000-9,000                | First 250 steps                   | PE parsing & feature cache stabilization           |

Table 7: Statistical Summaries, Uncertainty Measures, and Multiple-Comparison Controls by Analysis Target

| Analysis target              | Summary reported          | Uncertainty               | Effect size                 | Multiplicity control          |

|------------------------------|---------------------------|---------------------------|-----------------------------|-------------------------------|

| Tokens/s, step time idle %   | ' Median, IQR             | 95% bootstrap Cl<br>(10k) | Cliff's delta<br>(pairwise) | Holm-Bonferroni per<br>figure |

| HBM util, stalls, L2 traffic | <sup>2</sup> Median, IQR  | 95% bootstrap CI          | Hodges–<br>Lehmann $\Delta$ | Holm-Bonferroni               |

| Scaling efficiency curves    | Median line +<br>band     | BCa bootstrap             | _                           | Global Holm over cohorts      |